在设计上使用串阻的场景大家都见得多了,基本上很多1GHz以下的单端信号都有可能用到。从信号类型来看,像低速点的I2C信号、local bus信号到高一点的flash信号、以太网RGMII信号,甚至再高一点的DDR1到DDR2的数据信号,都能看到串阻的身影。

以RGMII为例,单根信号的速率大概是250Mbps,是非常典型的需要加串阻的应用场景。那各位硬件工程师或者设计工程师,你们印象中的串阻的阻值一般是多少呢,是不是就是22欧姆或者33欧姆呢?不知道大家有没有想过为什么基本就是这两个值,或者基本就是在22到33欧姆这个范围呢?这里面到底隐藏着什么理论,Chris将给大家仔细说说!

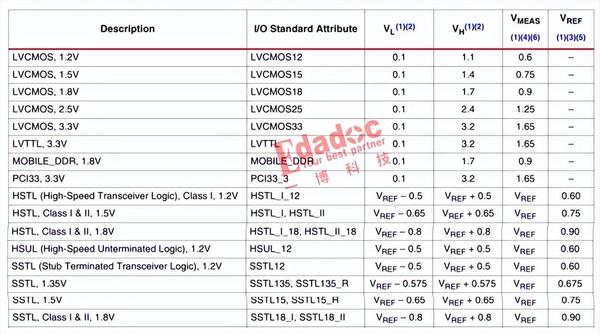

首先大家需要知道的是,像上面说到的这一类型的信号,主要的电平标准都八九不离十,就是下面的这些。

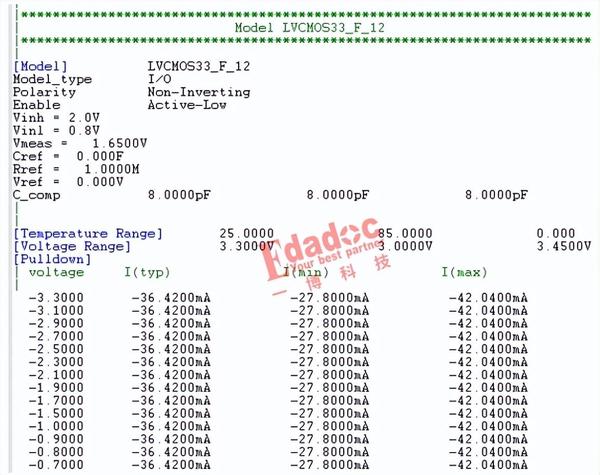

不同的电平标准从表现上看就是电平不同,还有就是上升时间不一样。我们拿今天要研究的LVCMOS电平为例来说,我们找到一个具有该电平标准的ibis模型,看看LVCMOS电平的一些电性能参数。

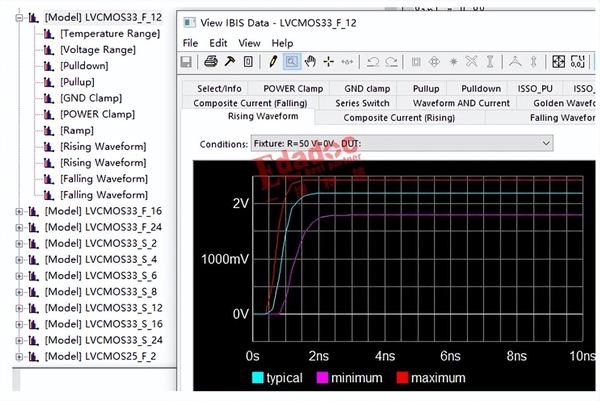

上面除了说明该电平的电压标准,阈值范围外,更重要的其实记载着该电平的输入输出的行为特性,也就是俗称的V-T曲线。例如我们打开与本文强相关的rising waveform这一项,里面可以看到它关于切换电平的特性。

看到这,我相信大家还是没弄懂,看这玩意到底跟要解释在设计上加多少欧姆的串阻有什么关系呢?

Chris不妨先问问大家,在设计上加串阻的作用是什么?这个大家估计都比较了解了,就是为了改善源端信号的反射,详细的原理大家可以回顾下这篇文章(*链接《PCB设计仿真之探讨源端串联端接》*)。

PCB设计仿真之探讨源端串联端接www.edadoc.com/home/technology/detail/id/91.html

在里面提取到一个很重要的信息点,那就是我们在芯片发送端加的串阻的阻值其实是为了和芯片的内阻加起来等于50欧姆来成为最佳的端接方案。那么问题又来了,我们怎么知道芯片的内

阻是多少呢?这也是本文的核心问题,我们只有知道了芯片的内阻是多少,才能够去选择合适的串阻进行合理的端接,产生比较好的效果。

Chris今天就教大家如何从ibis模型中计算出芯片内阻!上面说了,ibis模型展示给大家是都是V-T曲线、I-T曲线,I-V曲线这些行为级的参数,我们只有从这些曲线去推导出该电平输出buffer

的内阻。具体怎么做呢?我们还是看回刚刚的rising waveform曲线,这张图里面有两个关键的点,一个是红的圈圈的芯片该buffer的测试验证环境,另外就是绿色圈圈的测试出来的值(我们看typical的值)。

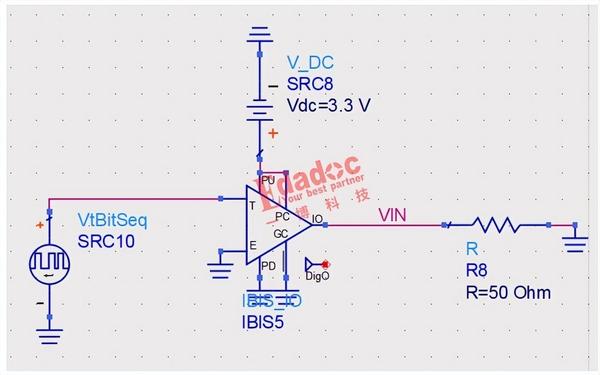

这张图描述的意思是这样的:测试环境是把该输出buffer接50欧姆电阻到地进行输出测试,然后去观测50欧姆电阻位置的值是2.18V左右,用仿真软件去搭建就是这个样子了。

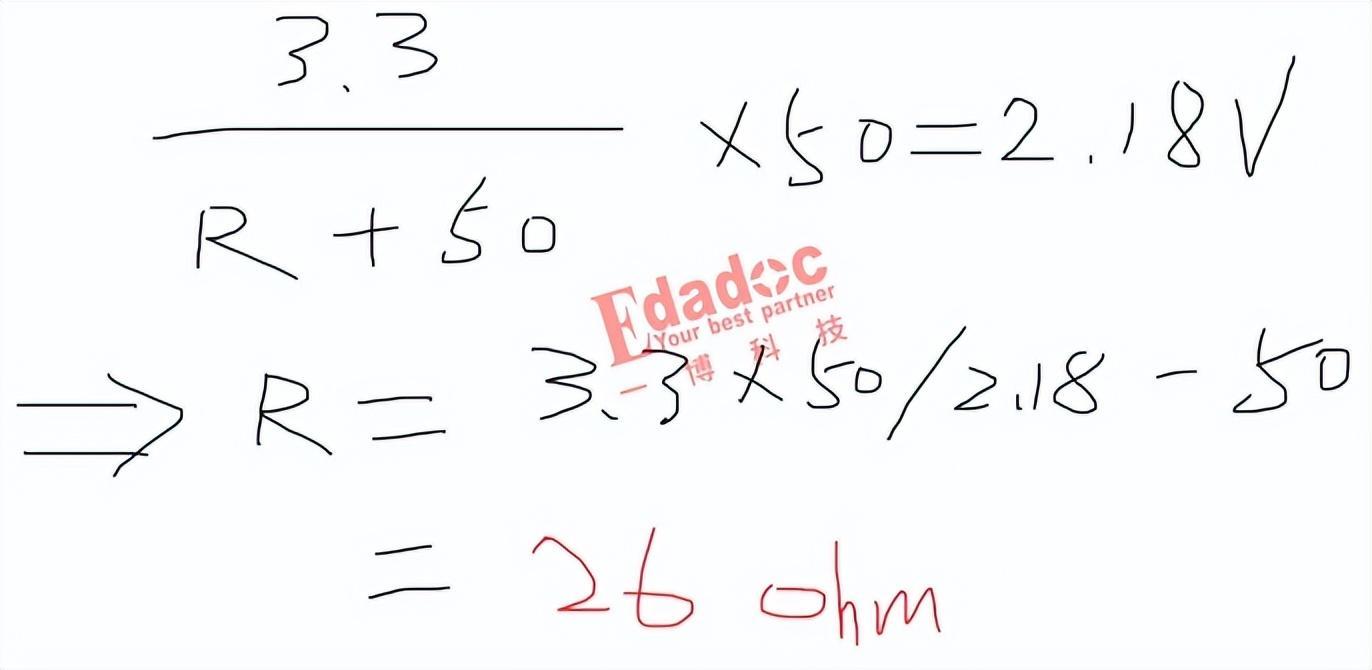

VIN的值测试出来就是2.18V,那么该buffer的内阻要怎么计算呢?其实原理就是把内阻R和50欧姆电阻进行分压,得到VIN是2.18V的过程。那么Chris大概在纸上算了下,得到的内阻就是这样的了。

嗯,其实也不是很难是吧,这个时候就推导出了该buffer的内阻大概是26欧姆的样子。其实你们多找几个不同电平的buffer去算算就会发现,内阻的范围大概也在17到30欧姆左右。因此大家也就知道了为什么我们无脑用22欧姆到33欧姆也基本能达到比较好的端接效果了。

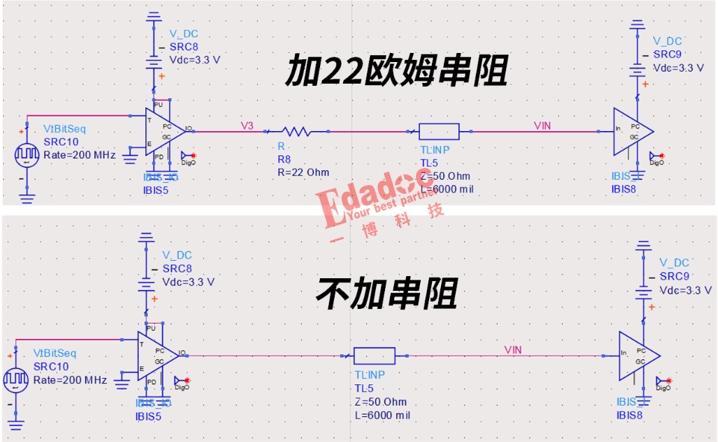

那在我们这个case中,使用这个电平buffer时,算出来的内阻是26欧姆左右,那我们就用一个22欧姆的串阻进行端接,加起来差不多就是50欧姆了,然后在200M的速率下看看加串阻和不加串阻的仿真结果对比!

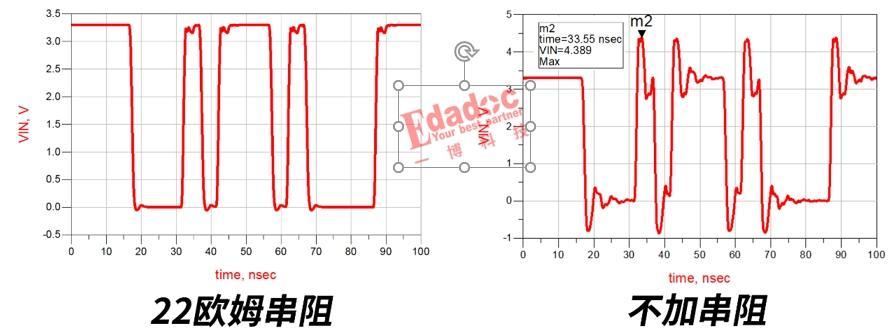

经过我们理论算出来的内阻,然后再去精确的配上合适的串阻后,大家从结果是就能看到接收端的波形是非常的理想,裕量大到没边,同时也能看到不加串阻时的过冲导致信号质量的恶化哈!

方法都是人想出来滴,通过这个方法来精确的进行串阻的端接,就能使信号的裕量更大,不然就只能还是继续拍脑袋来放串阻值了